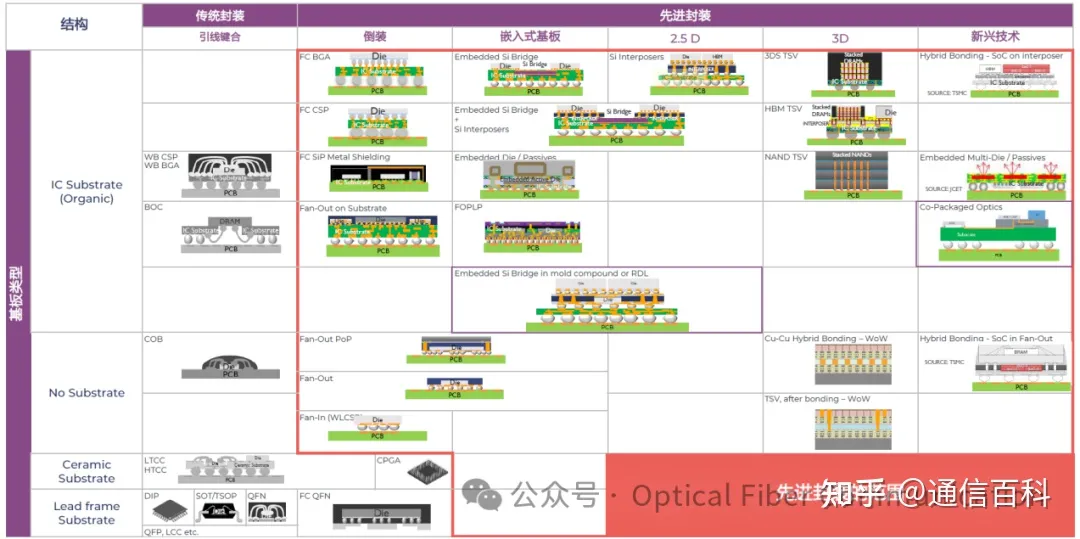

先进封装是对应于先进圆晶制程而衍生出来的概念,一般指将不同系统集成到同一封装内以实现更高效系统效率的封装技术。换言之,只要该封装技术能够实现芯片整体性能(包括传输速度、运算速度等)的提升,就可以视为是先进封装。与之对应的传统封装则是将各个芯片单独封装好,再将这些单独的封装芯片装配到PCB 主板上构成完整的系统,通过 PCB 板形成电信号之间的互连。

在工业界,一般将芯片的正装封装划分为传统封装,芯片与芯片(芯片与 PCB 板)之间通过键合金丝进行连接。而先进封装一般指倒装的封装形式,芯片与芯片(芯片与 PCB 板)之间通过焊球进行互连。

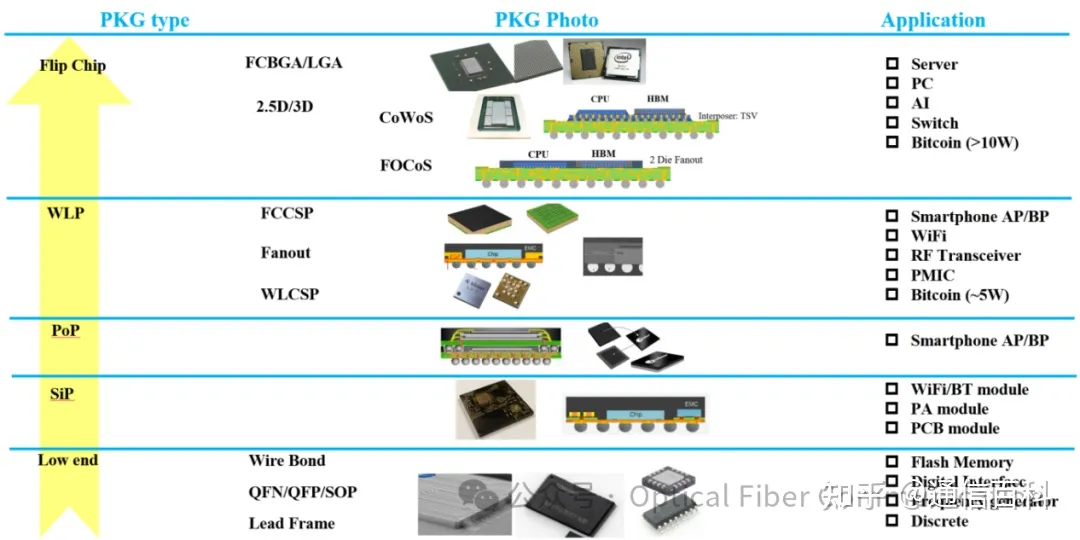

通常来说,芯片间的信息传输距离越长,信息传递越慢,芯片组系统的性能就越低。因此,同一芯片水平下,先进封装的传输距离更短,对应系统的性能越强。先进封装可以粗略地分为两大类,即倒装(Flip Chip)和晶圆级封装(Wafer Level Package,简称 WLP)。

近年来,基于这两大类封装形式,又衍生出多种具体的封装工艺,包括 FCBGA、FCLGA、2.5D/3D 封装、Fanout、FCCSP 等。尽管很多先进封装技术只有微小的区别,但是由于不同应用领域的客户的产品定制化的需求,行业中出现大量的不同种类的先进封装。

从下游应用来看,诸如服务器、AI 芯片、PC、交换机、大功率的矿机等需要高传输速率的应用场景大多采用 Flip Chip 形式的封装工艺,而智能手机、WiFi、射频芯片、电源管理芯片、小功率的矿机则通常采用 WLP 形式的封装工艺。对于闪存、分立器件等低传输、低算力应用场景仅需要用到打线(Wire Bond)形式、引脚(QFN/QFP/SOP)形式或者引线框架形式的传统封装。

典型先进封装形式,如高性能芯片常用封装:FCBGA

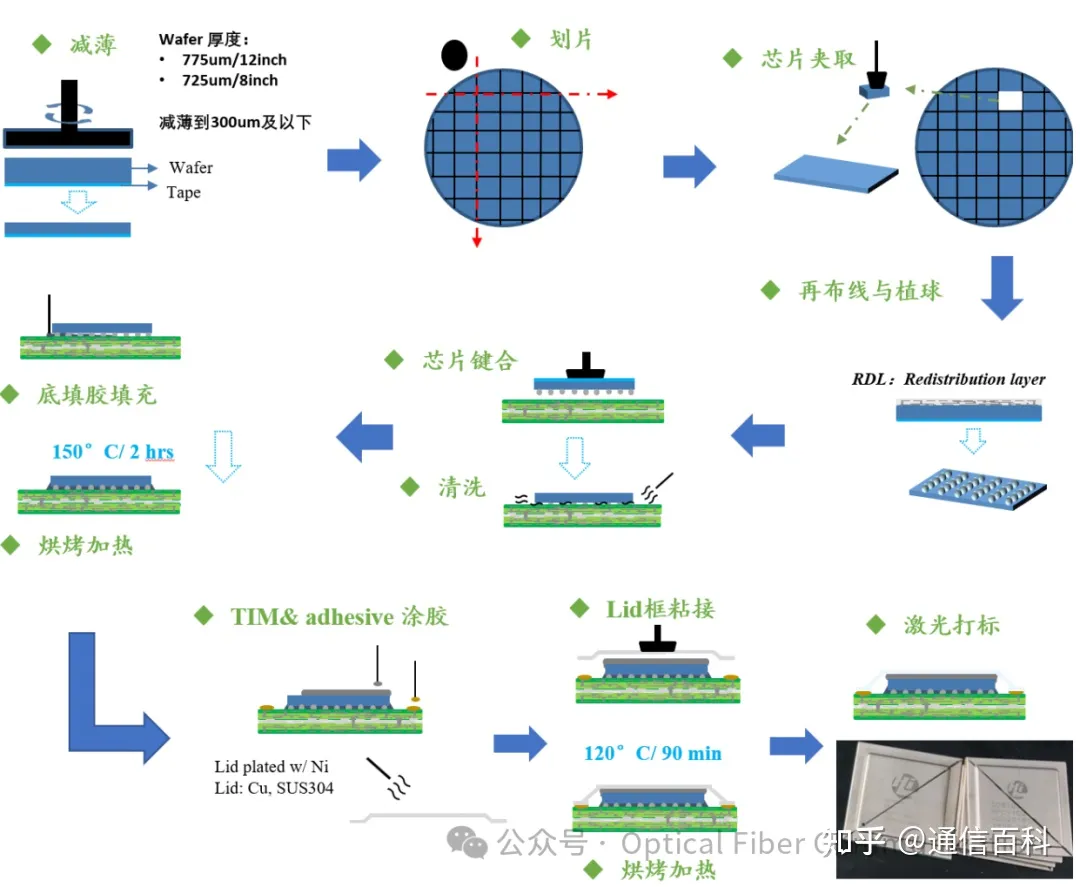

倒装作为先进封装的典型工艺,在 FCBGA、CoWoS、3D 封装等高端封装形式中具有重要作用。FCBGA 作为流程最简单的倒装封装工艺之一,理解其封装流程有助于了解更高端的 CoWoS 封装,大致可以将 FCBGA 封装流程分为以下几个部分:

(1)芯片背面减薄:wafer 从晶圆厂送到封装厂后,首先要做的是通过研磨减薄机对其厚度进行降低。在 wafer 制作过程中,晶圆厚度一般在毫米级别,需要减薄到300um 以下才方便后续的划片切割。减薄过程中需要向下施加压力,晶圆的正面需要用 UV 膜进行保护,防止正面晶体管破损。

(2)晶圆切割:可通过激光或者机械的方式对晶圆进行切割划片,此时正面同样需要贴上一层 UV 划片膜以防止切割边缘应力过大造成的芯片破损。

(3)再布线(RDL)与植球:取出单颗芯片,在正面进行 RDL 工艺,通过光刻、刻蚀、镀膜、清洗等工艺,制备出多层结构,以达到芯片线路重整化的目的。再将焊球放在对应焊点,加热后固定。

(4)芯片键合:固晶机将芯片与载板通过热压键合(TCB)的方式进行固定连接,然后将多余的助焊剂等试剂清除。

(5)填充底填胶:芯片键合后,焊球之间存在空气间隙,由于芯片和载板的热膨胀系数不同,芯片工作时发热,将造成芯片和载板不同程度的膨胀,进而拉扯焊球,将其拉断,影响芯片正常工作。因此将常温下是液态的底部填充胶(underfill)滴在芯片边缘,毛细效应下底填胶自动流进芯片间缝隙,加热固化后可以保护焊球。

(6)热界面材料(TIM)与粘接胶(Adhesive)涂胶:芯片背面涂上一层 TIM 胶以增强散热,同时在载板周围涂上一层 AD 胶,便于后续粘接散热盖。

(7)散热盖粘接:将金属散热盖与芯片贴合,烘烤加热后 AD 胶固化。

(8)激光打标:通过激光的方式在金属散热盖表面进行打标,完成整个 FCBGA 封装流程。

另一种是高效率封装形式:Fan-out

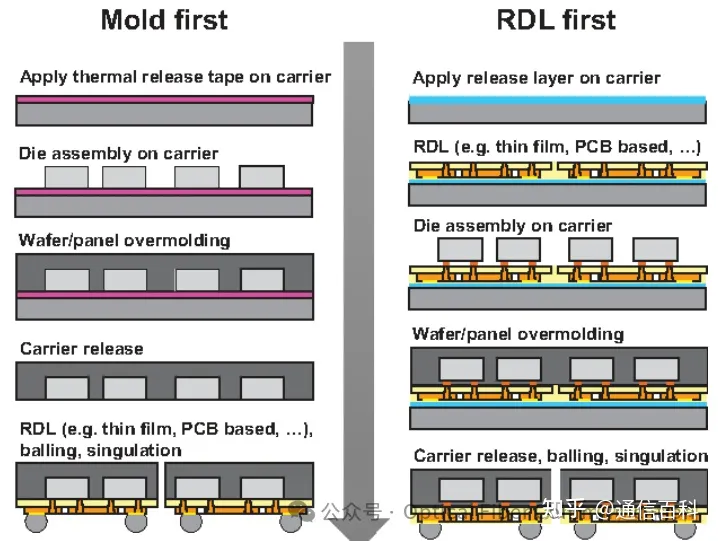

与 FCBGA 封装先切片后键合不同,晶圆级封装是先将整片晶圆封装过程完成后再进行切片,整体效率会高很多。晶圆级封装主要分为 Fan-in 和 Fan-out 两大类。传统的 WLP 封装多采用 Fan-in 型态,应用于低引脚(Pin)数的 IC,整体封装面积相较裸 Die 面积增加不大,成本相对较低。而与 Fan-in 相反,Fanout 凭借其低成本、高密度、轻薄化等优势占据重要地位。从细分类型来看,Fan-out 可分为 Mold first 和 RDL first 两大类,前者先对芯片进行塑封,再进行布线与植球;后者则先布线,再封装。

以 Mold first 类型为例,整个 Fan-out 封装流程分为以下几个部分:首先将热剥离胶带(thermal release tape)贴在载体晶圆(carrier wafer)上,然后拾取 KGD(known good die)并将其放置在载体上。接着使用塑封机让环氧塑封料包裹整个芯片,再将临时衬底去除。最后在芯片底部进行 RDL 工艺,再植上焊球。封装完成后再进行晶圆切割,就能得到所需要的芯片成品。

先进制程受限下破局之法:Chiplet

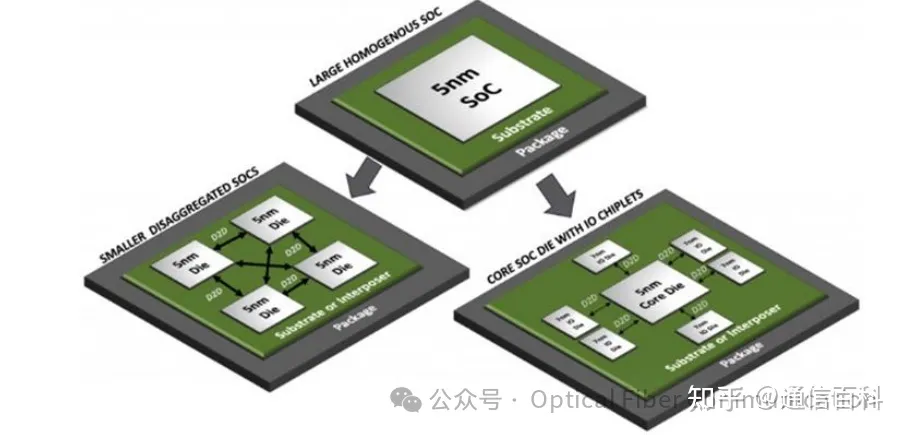

何谓 Chiplet?Chiplet 即小芯片之意,指在晶圆端将原本一颗“大”芯片(Die)拆解成几个“小”芯片(Die),因单个拆解后的“小”芯片在功能上是不完整的,需通过封装,重新将各个“小”芯片组合起来,功能上还原原来“大”芯片的功能。Chiplet 可以将一颗大芯片拆解设计成几颗与之有相同制程的小芯片,也可以将其拆解成设计成几颗拥有不同制程的小芯片。

并非具体封装工艺,更倾向于封装思路。严格意义来说,Chiplet 并不代表某一具体的封装形式或者封装工艺,而是体现先进封装的一种思路。除了将一颗大芯片切成多颗小芯片,再封装回去实现功能完整化的“同构”型 Chiplet,还有将不同类型芯片封装在一个载板上的“异构”型 Chiplet。通过 Chiplet 这一封装思路,可以:

(1)在先进制程不可获得的情况下,通过芯片堆叠(先进封转/Chiplet)和计算架构重构,以维持产品性能。(2)释放国内先进制程产能,有助于弥补制程的稀缺性。

因此,基于 Chiplet 的封装思路,叠加前述的 FCBGA 与 Fan-out 这两类基础封装工艺,已经实现了如 CoWoS、InFO、SoIC、EMIB、Foveros 等诸多更加高密度的封装工艺。