若您对半导体/芯片/光器件模块/光纤通信等感兴趣

欢迎关注我们!

随着摩尔定律逐渐放缓,把所有功能都塞进一个单一大芯片里,不仅技术上越来越难,成本也越来越高。这迫使整个行业寻找新的出路,而目前最重要的方向就是 “异构集成”。

啥是异构集成?

简单理解,咱们不硬搞单一大芯片了。而是换个思路,用先进的封装技术,把CPU、GPU、内存等这些不同功能的模块,像拼乐高一样,都集成到同一个封装里面。

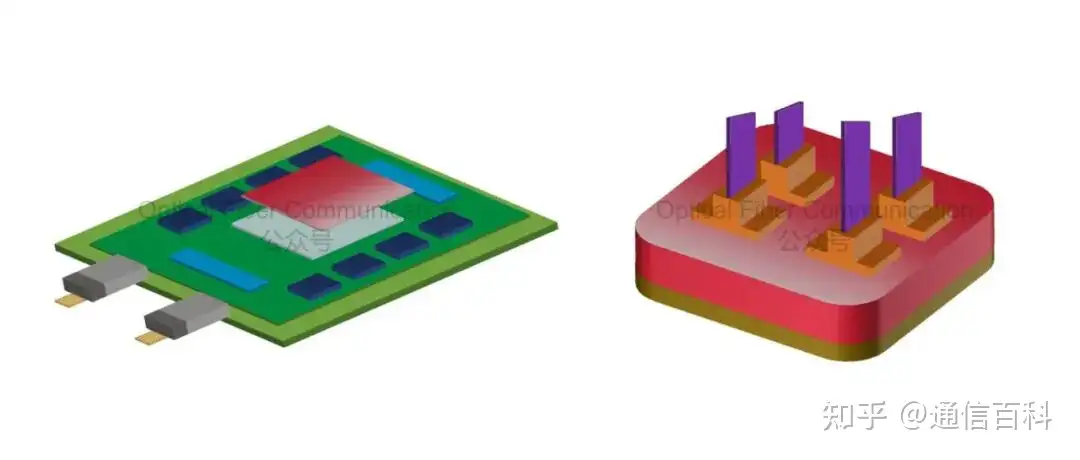

异质异构系统级混合封装工艺

当前,台积电的CoWoS、英特尔的Foveros和三星的X-Cube,构成了三种主流的先进封装解决方案。

台积电(TSMC)的CoWoS:

英特尔(Intel)的Foveros:

三星(Samsung)的X-Cube:

但它们的具体做法不太一样。下面我们从封装架构集成方法、互连密度与性能、设计复杂性与灵活性以及商业应用与部署等方面来阐述。

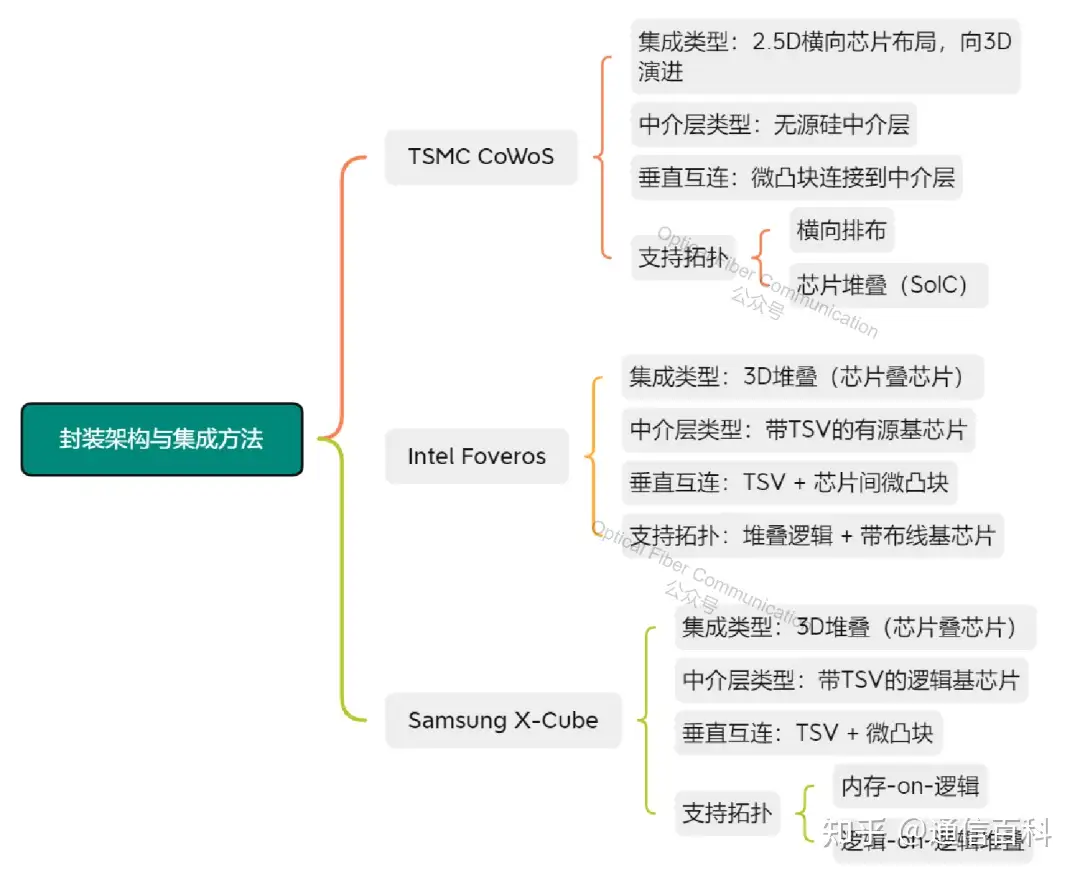

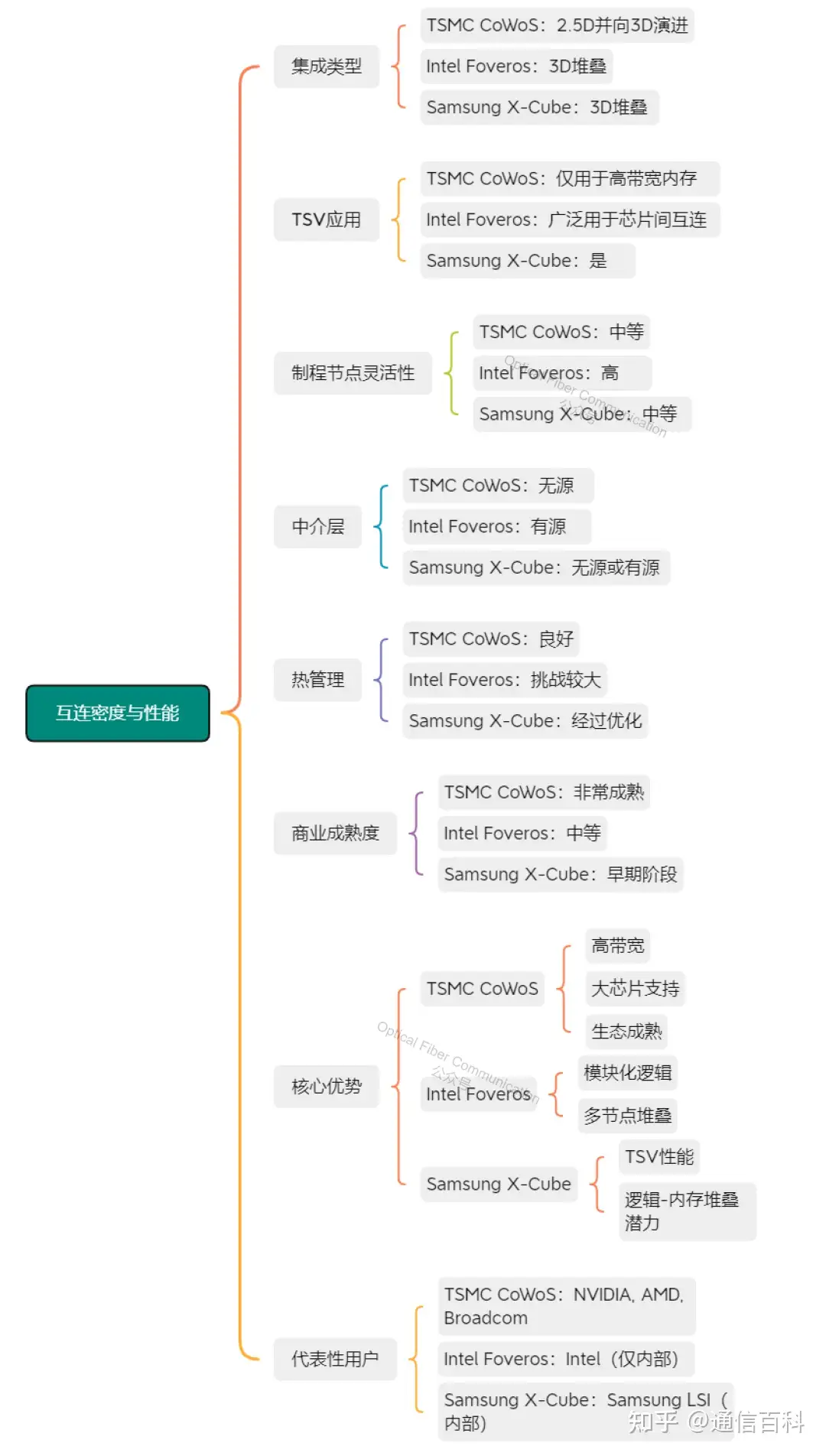

从封装架构集成方法来看:

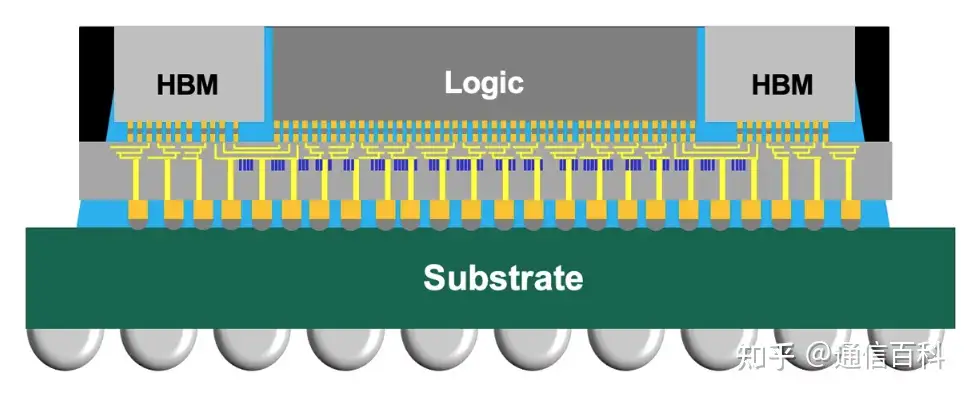

- TSMC CoWoS:

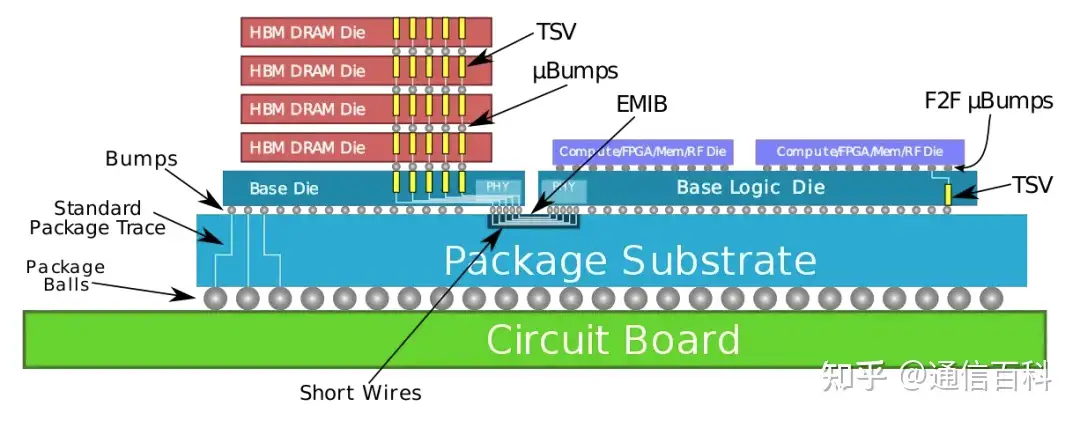

采用“芯片-晶圆-基板”架构,实现芯片间极高带宽与信号密度。具备优异扩展性,支持光罩尺寸中介层(如CoWoS-S),并与台积电3D堆叠方案SoIC协同。

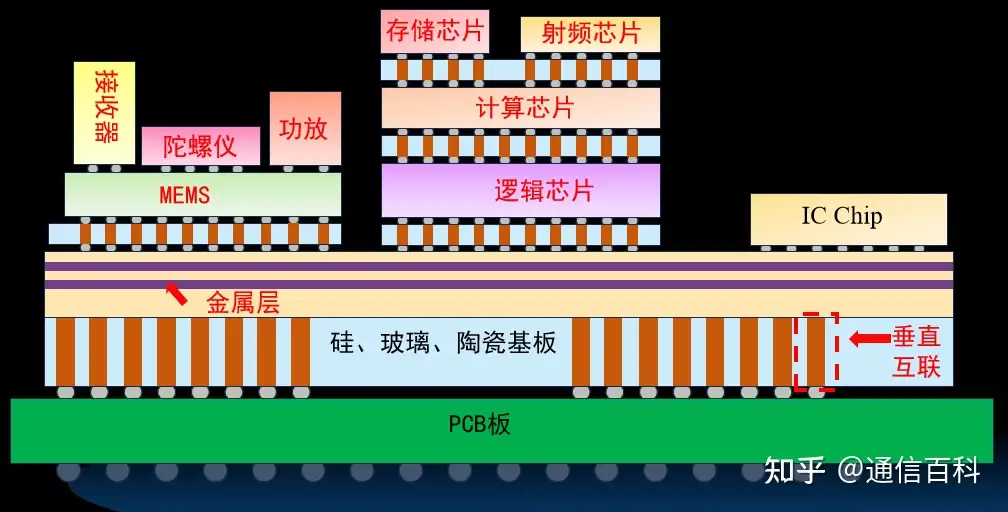

- Intel Foveros:

业界首款量产逻辑-on-逻辑3D堆叠技术,依赖TSV与细间距微凸块实现互连,支持多工艺节点模块化集成,已用于Meteor Lake客户端CPU及后续AI加速器。

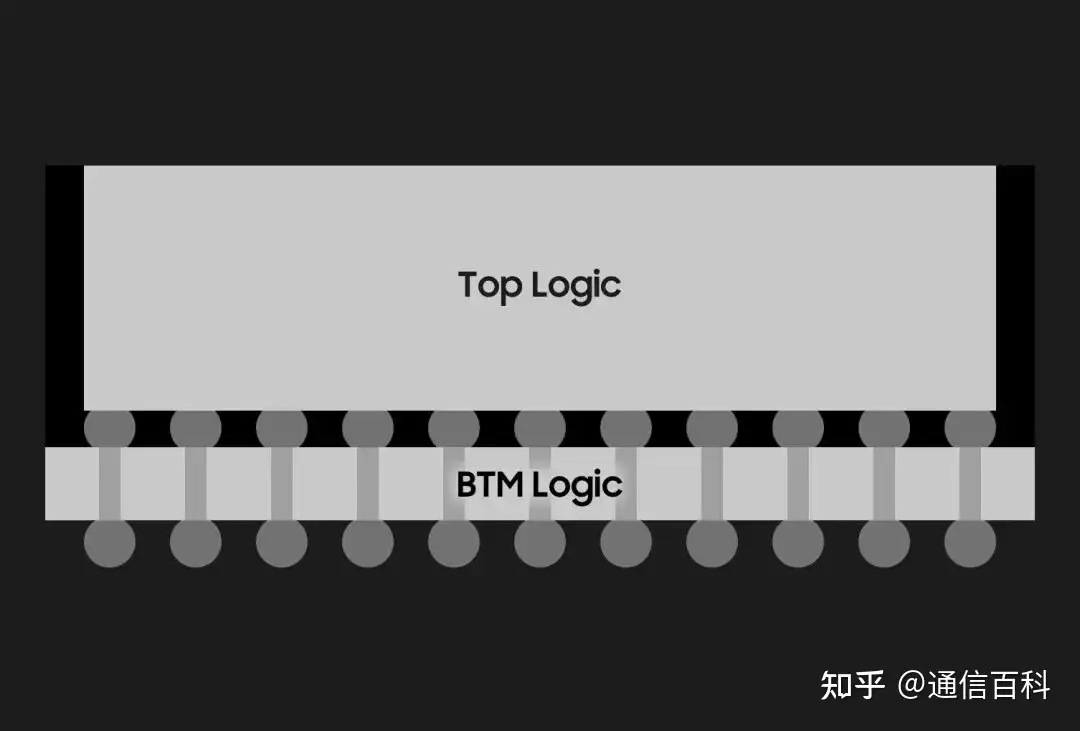

- Samsung X-Cube:

采用极细TSV间距与紧密微凸块间隔,通过TSV优化与协同设计提升热控制与信号完整性,目前处于原型与研发阶段,尚未大规模商用。

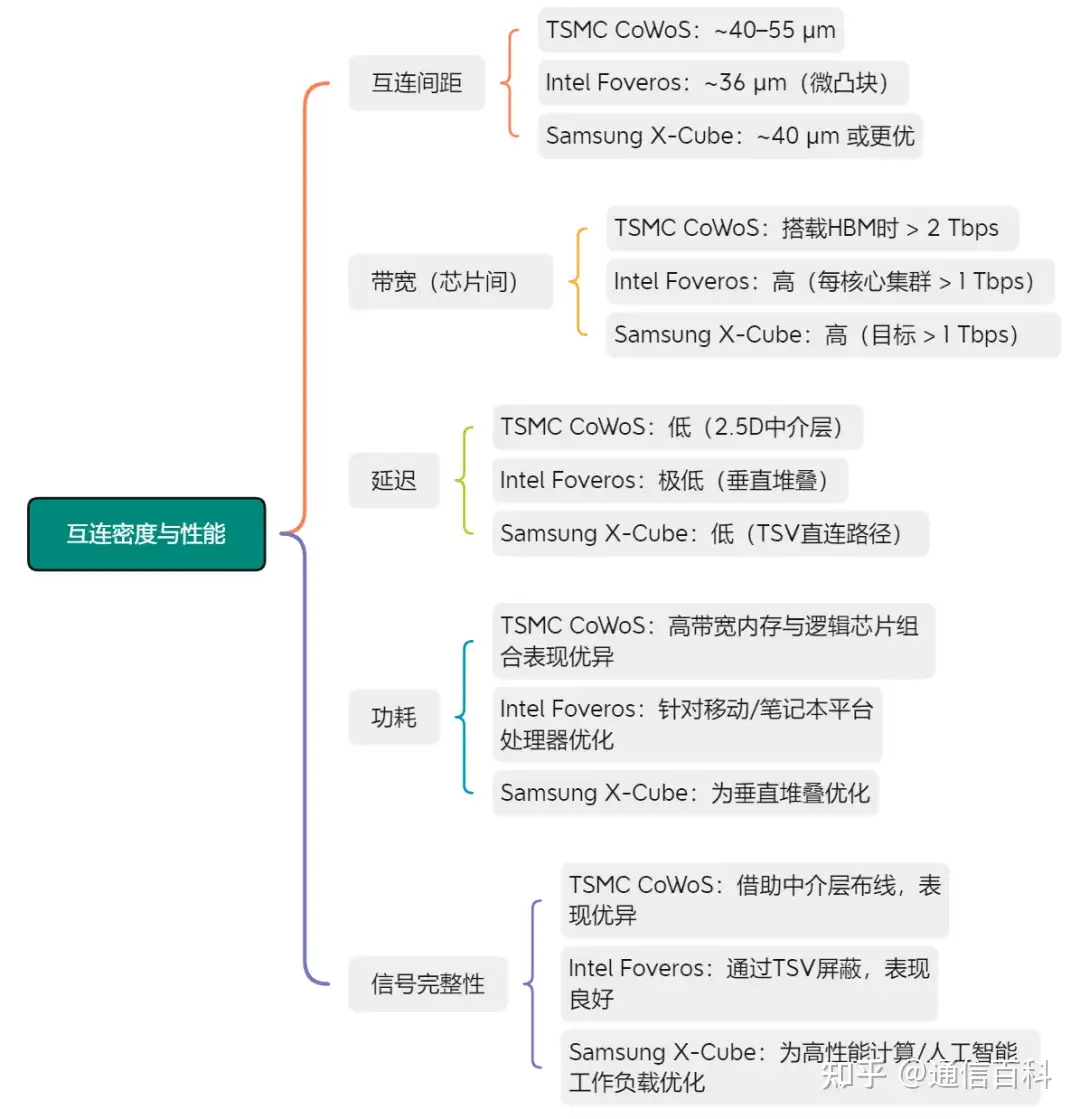

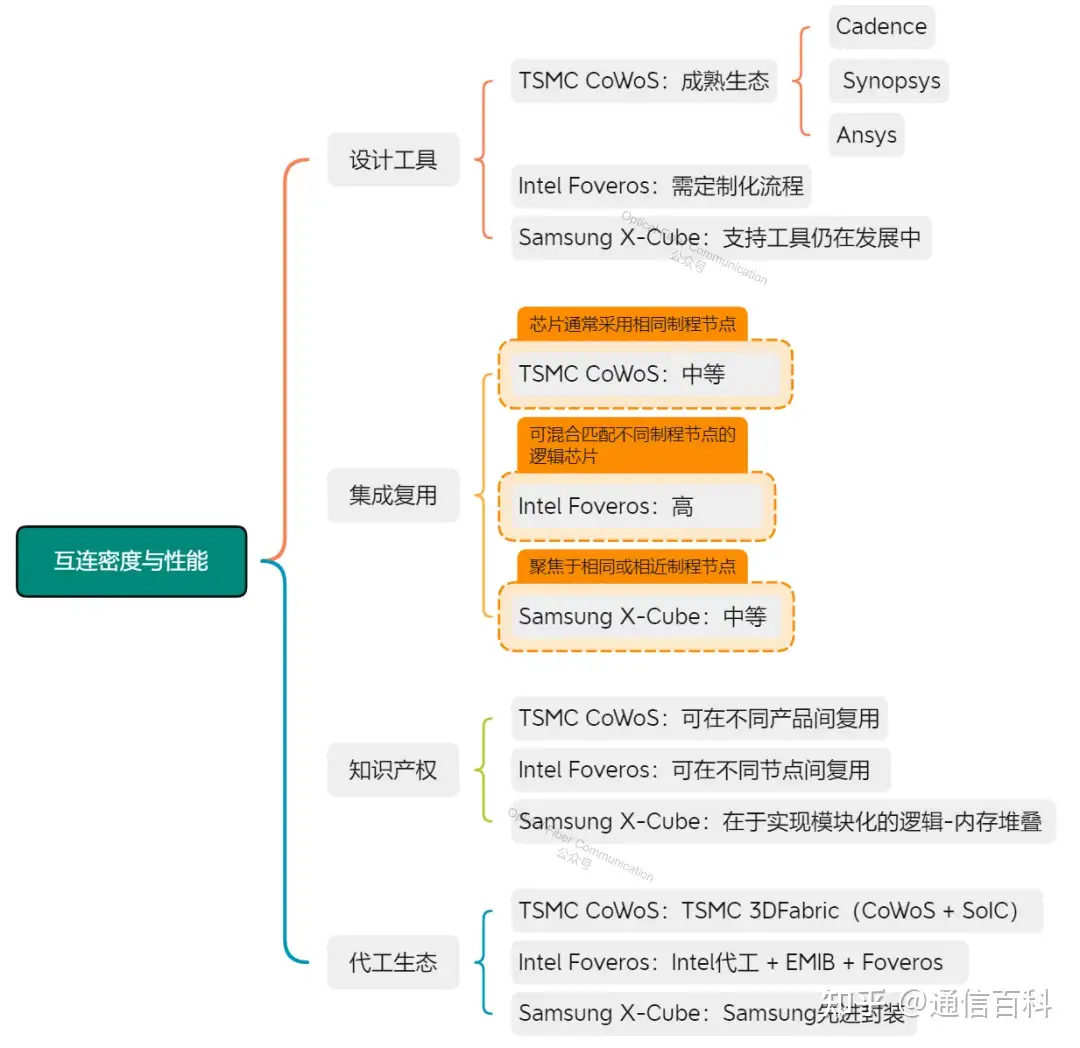

在互连密度与性能方面的对比如下:

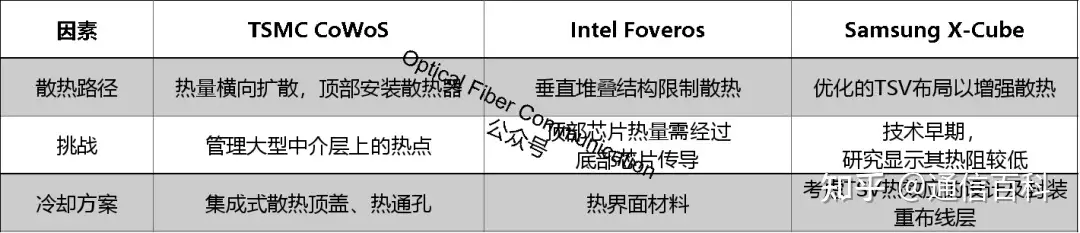

热管理是先进封装的关键考量,各方案特点如下:

由于逻辑芯片堆叠会显著提升功率密度,Foveros技术面临更严峻的热约束挑战。CoWoS得益于芯片的横向排列与热量的扩散,拥有更充裕的热管理空间。X-Cube则试图通过优化TSV的布局来改善垂直方向的导热性能。

在设计复杂性与灵活性方面,各平台存在差异:

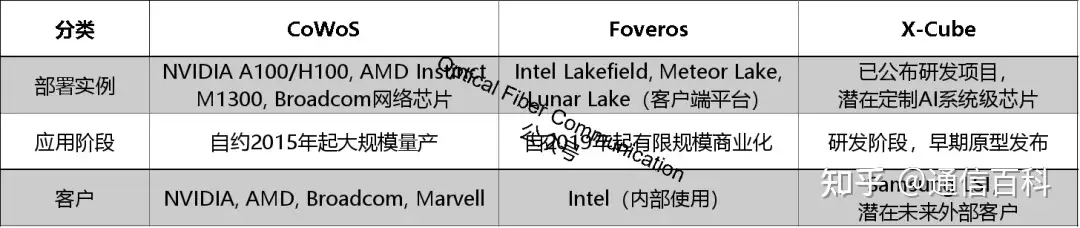

商业应用与部署情况如下:

从战略层面看:

- TSMC CoWoS主导着高性能计算与人工智能市场,是NVIDIA保持GPU领导地位的关键推手,并构成了TSMC 3DFabric平台的基础。

- Intel Foveros对Intel的模块化设计战略至关重要,其应用正从客户端扩展至数据中心与AI加速器,未来将与嵌入式多芯片互连桥接技术结合。

- Samsung X-Cube是Samsung争夺封装技术领导地位的发力点,与其高带宽内存业务紧密协同,重点面向未来高性能计算与移动设计中的逻辑-内存共封装。

总结性对比表如下:

最后我们来看看三家的技术发展时间线:

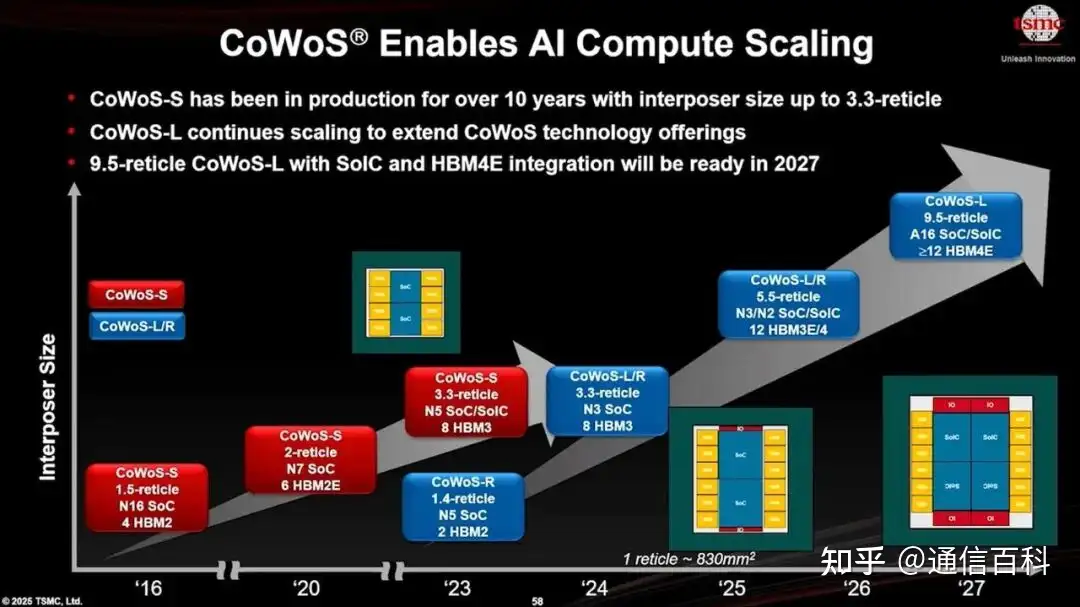

- TSMC- CoWoS 系列

- 2011 年:推出 CoWoS(Chip on Wafer on Substrate)技术;

- 2012 年:量产首颗基于 CoWoS 的芯片,为 Xilinx FPGA;

- 2015 年:CoWoS 技术应用于 NVIDIA Pascal 架构产品;

- 2017 年:发布升级版本 CoWoS-S;

- 2020 年:推出 SoIC技术,作为 CoWoS 的 3D 封装补充方案;

- 2022 年:发布 CoWoS-R 版本;

- 2024-25 年:规划推出 CoWoS-3D 与 SoIC-Direct 技术。

- Intel- Foveros 系列

- 2018 年:公开公布 Foveros 3D 堆叠封装技术;

- 2019 年:基于 Foveros 技术的首款产品 Lakefield 处理器量产;

- 2022 年:预览采用 Foveros 技术的 Meteor Lake 处理器;

- 2024 年:正式发布 Meteor Lake 处理器;

- 2025 年:规划推出 Lunar Lake、Falcon Shores 两款基于 Foveros 技术的产品。

- Samsung- X-Cube 系列

- 2019 年:启动 X-Cube 3D 封装技术内部开发;

- 2020 年:公开宣布 X-Cube 技术;

- 2021 年:推出基于 X-Cube 的 EUV 演示芯片;

- 2023 年:开展 HBM3 内存堆叠试点项目(基于 X-Cube 技术);

- 2025 年:目标实现 AI / 高性能计算领域的逻辑 – 内存堆叠(基于 X-Cube 技术)。

感谢阅读!