经公众号Optical Fiber Communication同意发布。

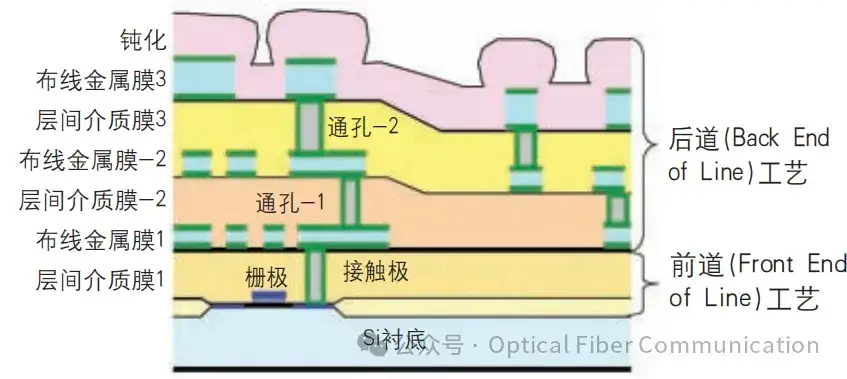

为了实现更多的功能和更高的性能,我们会在芯片上搭建起层层叠叠的线路。这就是我们常说的多层布线技术。

但与此同时,它也带来了一个挑战:每增加一层线路,就像在原本平滑的地面上堆砌砖块,使得芯片表面变得坑坑洼洼。这种不平整的表面不仅影响了电流的传输效率,还可能引发一系列缺陷和故障,对后续的制造工艺构成了不小的威胁。

因此,如何让这些层次都平整,成为了芯片制造领域亟待解决的问题。而CMP工艺,正是解决这一问题的关键所在。首先,我们来聊聊CMP工艺产生的历史背景。随着系统级LSI和先进CMOS数字电路的发展,多层布线化的趋势越来越明显。多层布线就像是在芯片上搭建的一座座高楼,楼层越高,就越需要坚实的基础和平整的地基。而CMP工艺,就是为这座“芯片高楼”打造坚实地基的“工程师”。

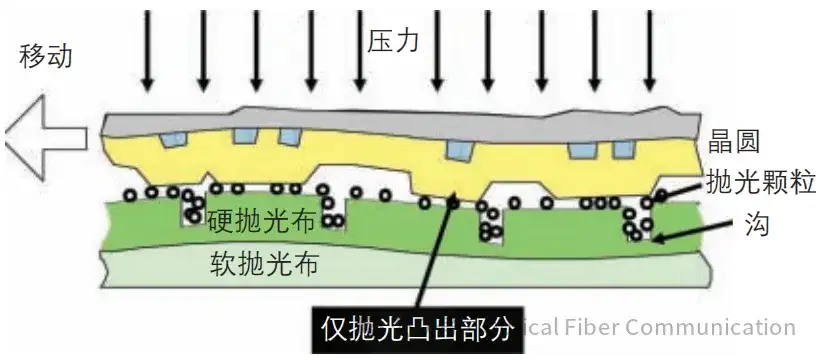

在存储器中,由于内存单元的结构相对简单,通常只需要2层位线和字线的走线,因此有时不需要使用CMP工艺。但在更复杂的数字电路中,情况就完全不同了。为了快速完成设计并验证其可靠性,我们通常会采用Building Block方式,将已经验证过的电路模块像搭积木一样组合起来。这样一来,布线就必然形成了层次化结构,也就需要多层布线。而多层布线带来的表面不平整问题,就需要CMP工艺来解决了。CMP主要运用化学刻蚀和机械抛光的双重作用,将硅片表面的凸起和凹陷都磨平,让表面变得光滑如镜。这样,电流在传输时就能更加顺畅,从而提高芯片的性能。同时,平整的表面也能减少缺陷和故障的发生,提高芯片的可靠性。

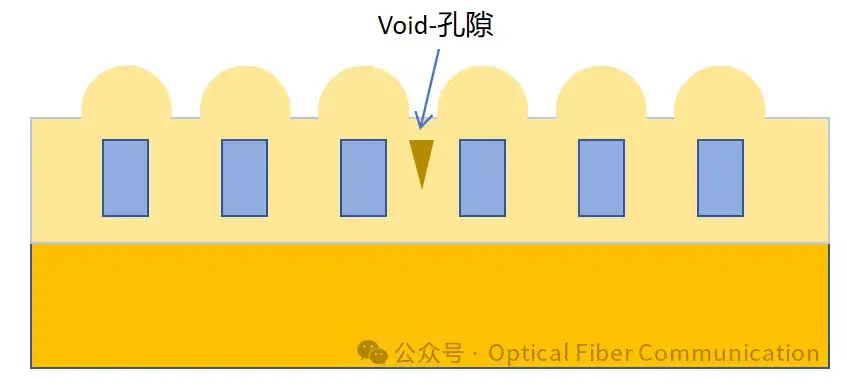

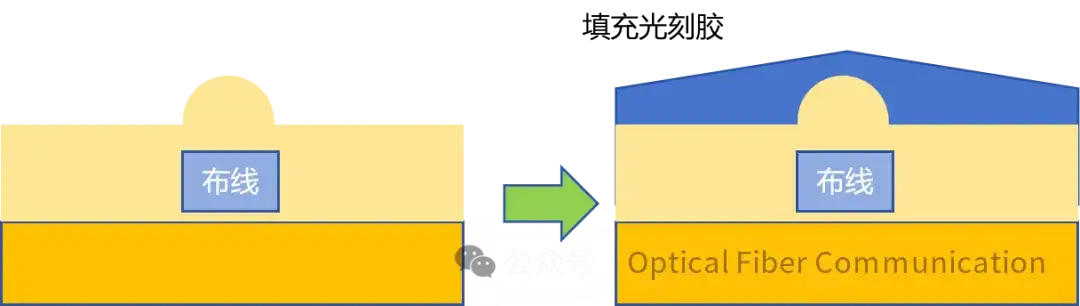

其实,在CMP工艺实用化之前,人们已经尝试过其他平坦化技术。但在20世纪80年代到90年代,这些技术都面临着一些难题。比如,随着布线宽度和间距的缩小,层间绝缘膜很难完全填满布线之间的空隙,导致“Void”孔隙的出现,这会严重影响芯片的可靠性。为了解决这个问题,人们发明了间隙填充技术。然而,这种技术虽然能够解决一部分问题,但并不能完全实现表面的平坦化。

除了表面平坦化,布线台阶如何平坦化也是一个大问题。尽管有一些技术,比如涂布型的层间绝缘膜平滑化和光刻回蚀技术,但这些方法都无法达到完全平坦化的效果。布线台阶的存在不仅影响了电流的传输效率,还可能引发一系列制造问题。

这里,我们需要知道,化学刻蚀和机械抛光的结合才是减低台阶绝对高度的最好的平坦化技术。另一个方面,咱们的光刻机也需要用到CMP技术,作为芯片制造中的关键设备。如果在光刻过程中,芯片表面不平整,就会导致光刻图案的失真和变形,从而影响芯片的功能和性能。通过CMP工艺对芯片表面进行平坦化处理,可以确保光刻图案的精度和一致性,提高芯片制造的良品率和可靠性。此外,在CMOS电路的制造中,CMP工艺也发挥着不可替代的作用。CMOS电路结构复杂,布线层次多,因此表面不平整问题尤为突出,通过CMP工艺对CMOS电路表面进行平坦化处理,可以消除布线台阶和坑洼等缺陷,提高电路的稳定性和可靠性。可以说,没有CMP工艺,就无法制造器件。