我们知道,提高波特率会加快符号在信道中的传输速度,但可能导致信号衰减的增大。增加脉冲幅度调制方案(PAM)可使每个符号发送更多的比特,但误差幅度更低,阈值更严格。

国际组织 IEEE 和 OIF 都已着手在 224Gb/s 线路上定义 800G 和 1.6T。以下是实现800G 和 1.6T(基于224Gb/s 通道速率)的几个挑战和潜在解决方案。

- 交换机硅SerDes

更快的网络交换芯片对提高通道速度至关重要。高速特定应用集成电路(ASIC)可在服务器机架和数据中心的元件之间实现低延迟切换。从 2010年到 2022年,经过互补金属氧化物半导体 (CMOS) 工艺技术的多次改进,交换机硅带宽从 640Gb/s 提高到 51.2Tb/s。

SerDes(串行器/解串器)速度和SerDes的数量(I/O引脚)定义了芯片的带宽。例如,带宽为 51.2Tb/s 的芯片有 512 个 10Gb/s SerDes,足以支持 128 个端口的 400G 以太网容量,每个端口由四条 100Gb/s 通道组成。下一代交换机硅将再次把带宽翻倍,102.4T 交换机将拥有 512 个 200Gb/s SerDes 通道。这些硅交换机将通过 224Gb/s 通道支持 800G 和 1.6T。

- 脉冲幅度调制

提高符号率(波特率)会导致信号衰减,因为数据在信道中移动的速度更快。保持高速数字通信的信号完整性变得更加复杂,因此标准组织采用了更高的调制方案,以增加每个符号的比特数。例如,400G 以太网使用四级脉冲幅度调制 (PAM4) SerDes,在 50GBd 的相同符号速率下,将数据速率从 50Gb/s 提高到 100Gb/s。有了这一变化,400G 网络可以开始使用四通道 100Gb/s,而不是八通道 50Gb/s。

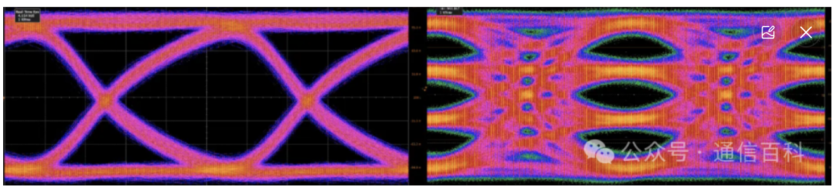

脉冲幅度调制需要权衡利弊。每个周期发送更多比特会降低每个符号的噪声余量。采用非归零(NRZ)信令时,区分零位和一位的电压阈值范围更高。随着每个符号比特数的增加,阈值会越来越小,抗噪能力也会下降。在 50GBd NRZ 条件下,噪声水平不会使眼图闭合,这意味着接收器可以清楚地区分比特水平,但对于试图解释 50 GBd PAM4 符号的接收器来说,这可能会带来麻烦。

图:NRZ 与 PAM4 的眼图比较

PAM4 信号的眼图高度较小,因此在噪声和抖动方面具有更小的设计裕量。目前,业界可能会保留 PAM4 的通用性,转而研究在高速条件下保持数据完整性的其他方法。但未来的标准可能会采用更高的调制方案(PAM6 或 PAM8)。800G光模块和光芯片投资价值几何?

- 前向纠错如何降低误码率?

在大多数高速数据标准中,发射器和接收器中经过微调的均衡器可确保通过信道传输的信号能在另一端被解读,从而补偿信道中的信号衰减。然而,随着速率进一步突破物理极限,需要采用更复杂的方法。

其中一种解决方案就是前向纠错。

前向纠错是指传输冗余数据,帮助接收器拼凑可能有损坏比特的信号。前向纠错算法通常能在发生随机误差时很好地恢复数据帧,但对于丢失整个数据帧的突发错误则效果不佳。

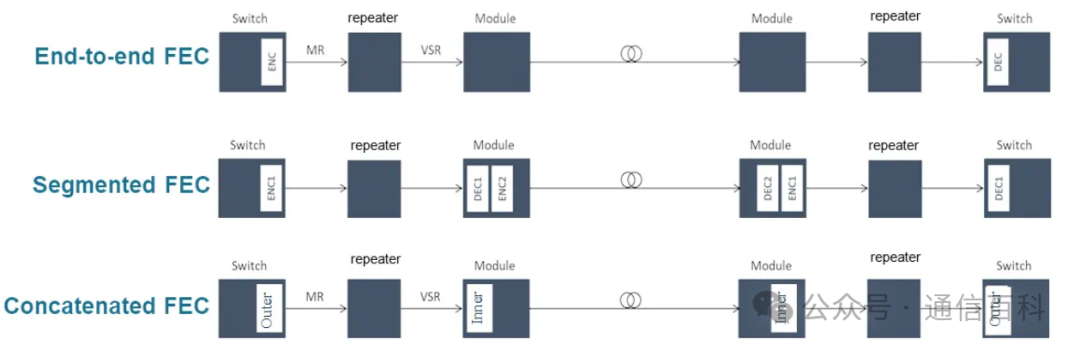

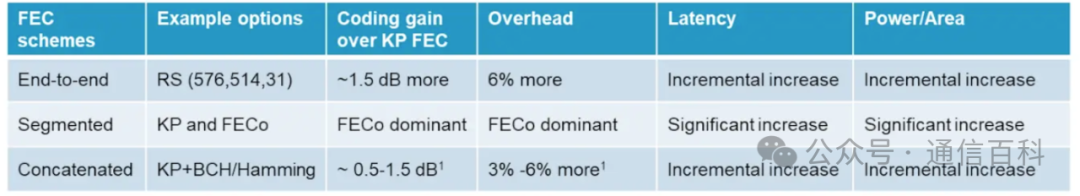

丢失整个数据帧会增加接收器重建信号的难度。例如,224Gb/s 收发器需要更强大的 FEC 算法才能成功收发数据。每种 FEC 架构都有编码增益、开销、延迟和能效方面的权衡和优势。

图:FEC 架构类型

图:不同FEC类型的权衡取舍

虽然 FEC 有助于减轻发送器和接收器之间随机误差的影响,但突发误差仍会造成问题。在 224Gb/s 系统中,必须采用更复杂的 FEC 算法才能最大限度地减少突发误差。测试和测量开发人员正在开发 FEC 感知接收器测试解决方案,以识别何时出现帧丢失并帮助调试。

800G光模块预期持续看好,国产光模块光芯片厂商或将持续收益

- 光模块如何影响能效?

数据中心面临的最严峻挑战可能就是功耗,即耗电量。数据中心的耗电量约占全球总发电量的 1%。数据中心运营商希望在不相应增加耗电量的情况下提高处理能力,而光模块是提高能效的关键部件之一。

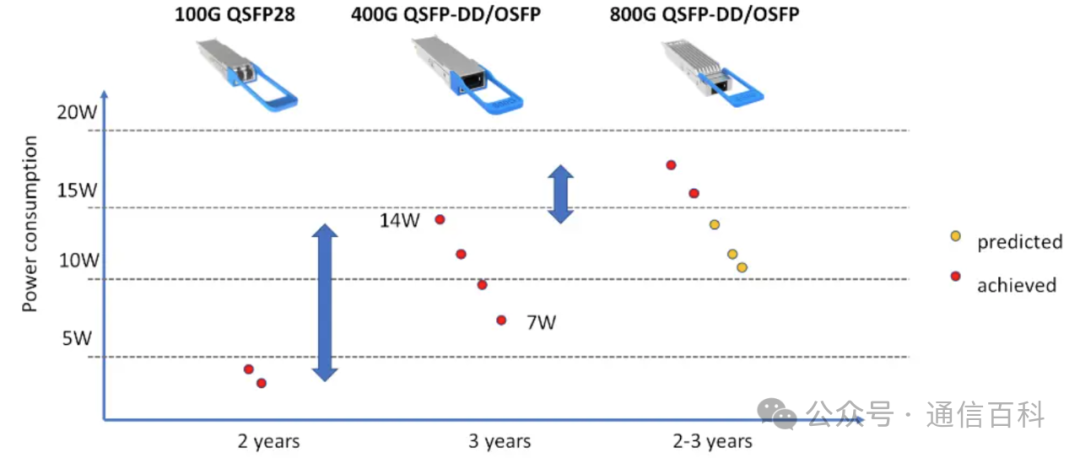

据我们了解,每一代光模块的功耗都在增加。例如,100G 可插拔模块(QSFP28)的功耗不到 5W,但 400G QSFP-DD模块的功耗则高达 14W。

当然,随着光模块设计的成熟,它们将变得更加节能。以 800G QSFP-DD 模块为例,其首次亮相时的功耗为 17W;随着技术的成熟,功耗应降至 10W。一般来说,每个Bit的功耗都在下降。但是,由于每个数据中心平均有 5万个光模块,模块的平均功耗越来越高,仍然是一个问题。

图:各代光模块之间的功耗(资料来源:Eoptolink)

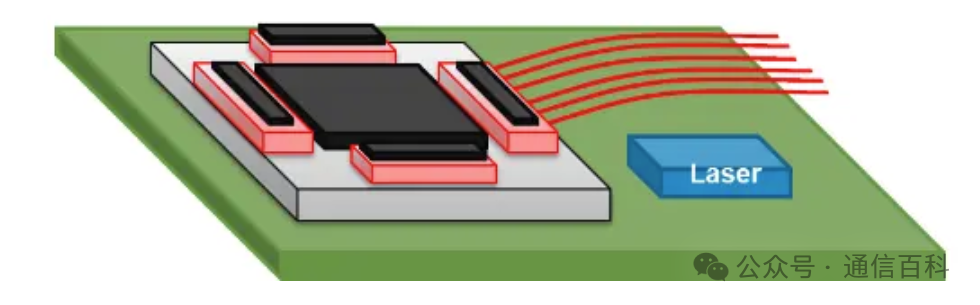

为了提高能效,研发人员正在研究替新的封装方案。CPO共封装光学器件(Co-packaged)有可能实现最低功耗。共封装光学器件将光学模块移至ASIC,省去了光学重定时器,并在封装内进行光电转换。这里的代价就是:功率耗散集中在 ASIC 封装内,这可能需要新的冷却解决方案。

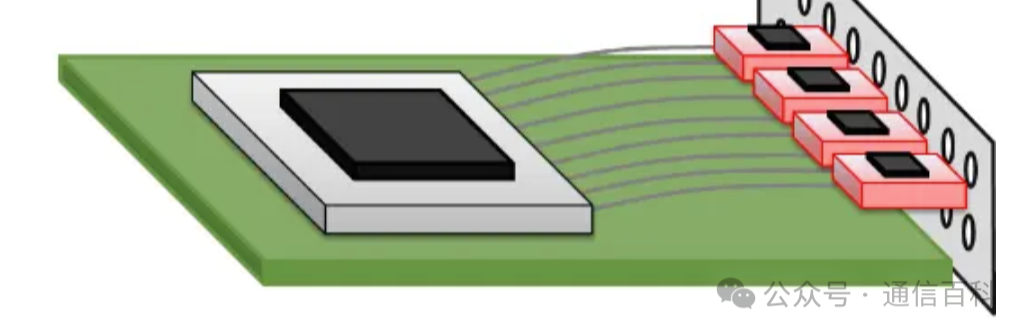

图:Pluggable可插拔模块

图:Co-packaged共封装模块

冷却是数据中心的另一个重要耗电因素。共封装光学器件正在研发中,因此业界可能会继续在 800G 系统中使用可插拔光学器件。800G 或 1.6T 标准的后续版本可能会使用共封装光学器件。

- 800G 和 1.6T 网络的时间表是什么?

虽然无法准确预测未来,但我们可以根据当前的网络研发状况提出一些看法。2022年,OIF 的 112Gb/s 标准和 IEEE 的 802.3ck(400G)标准最终发布。这些标准将为在 112Gb/s 通道上定义 800G 奠定基础。

在未来两年内,IEEE 和 OIF 将最终确定物理层标准,并将发布更多有关协同封装光学器件、1.6T 收发器和 224 Gb/s SerDes 交换芯片的消息,这将为使用 224 Gb/s 通道的 800G 和 1.6T 的最终验证奠定基础。

目前,400G 正在进行大规模部署。运营商将升级超大规模数据中心,以支持当前的需求浪潮。到 2025年,我们可能会看到 448Gb/s SerDes 芯片(使用102.4T ASIC)出现在市场上。到那时,我们可能就会讨论 3.2T的网络需求了。